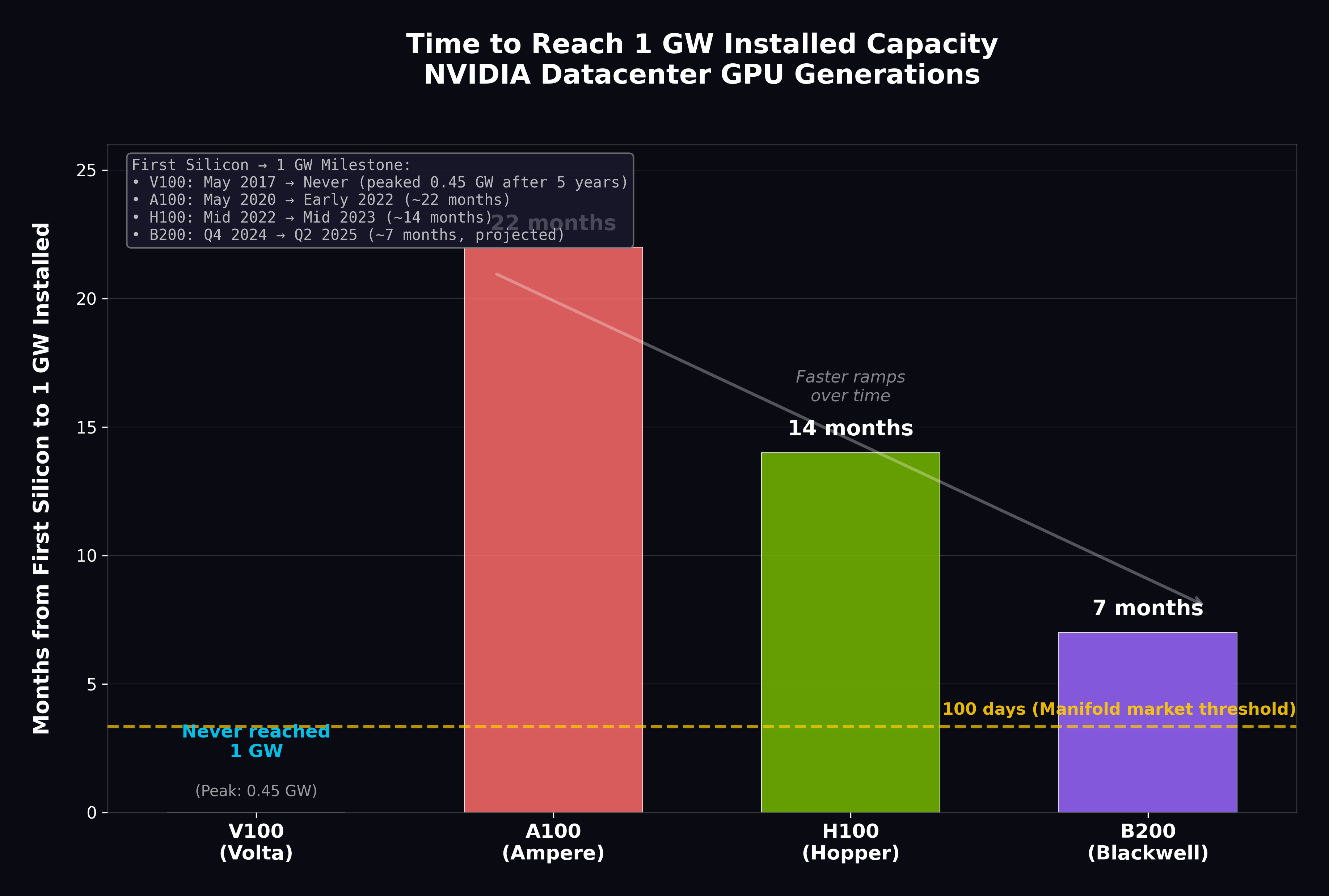

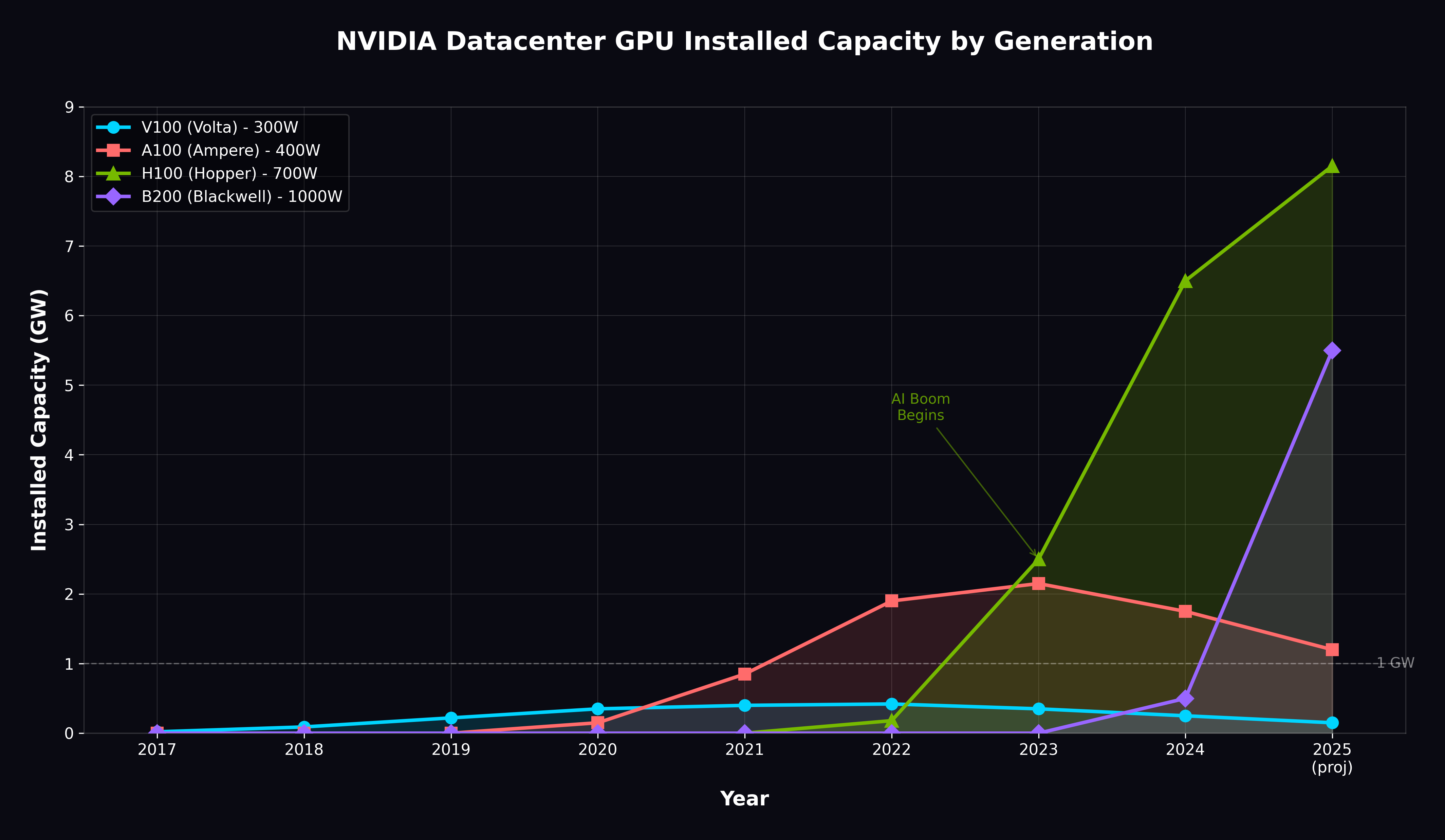

Resolves as YES if there is strong evidence that, before January 1st 2032, there exists at least one new AI accelerator chip series for which the elapsed time between (a) the date a first fully working chip from that series exists in silicon and (b) the date on which at least 1 gigawatt (1 GW) of nameplate power capacity from that series is installed in operational compute clusters worldwide is 100 days or fewer.

Core definitions

AI accelerator chip series (“series”)

A “series” is a family of data‑center‑class AI accelerators (GPUs, ASICs, wafer‑scale engines, multi‑die modules, etc.) from a single vendor that share the same underlying microarchitecture and base die design, even if they come in multiple SKUs.

Variants that differ only in memory size, binning, cooling, form factor, or minor packaging changes (e.g. PCIe vs SXM; 80GB vs 144GB; air vs liquid cooled) are treated as the same series.

A major architectural or die change (e.g. “Hopper” → “Blackwell”, “TPU v4” → “TPU v5”, “Ascend 910C” → “Ascend 910D” if based on a substantially new design) counts as a new series with its own clock.

If there’s ambiguity about whether two chip lines are one series or two, the resolver will choose the classification that is more conservative for resolving YES (i.e. makes it harder to satisfy the 100‑day condition).

What counts as an AI accelerator (scope)

Chips must be primarily marketed and used for training and/or inference of modern ML models in data centers, HPC clusters, or supercomputers.

General‑purpose CPUs, smartphone SoCs, tiny edge accelerators, and low‑power embedded chips do not count unless they are clearly positioned as high‑end AI accelerators; the intent is to track “big iron” AI compute, not commodity phone chips.

“First fully working chip exists in silicon” (T_start)

T_start is the earliest date after this market is created when there is strong public evidence that at least one fully functional chip from that series physically exists and is successfully running test or production workloads, either inside the vendor or at an external partner.

This can be evidenced by, for example, dated vendor announcements (“we have first silicon back and are running workloads”), conference demos on real hardware, or credible reporting that working samples are in use.

Purely simulated designs, partial test dies that are not representative of the production chip, or unverifiable rumors do not start the clock.

“1 GW of installed nameplate power capacity” (T_1GW)

We define installed capacity in terms of nameplate power, usually the chip’s thermal design power (TDP) as specified by the vendor, or reasonable equivalents when only system‑level numbers are public.

Chips from the series are counted toward the 1 GW threshold when they are installed in operational servers, racks, pods, or systems that are at least capable of being powered up for routine workloads, including:

The vendor’s own internal clusters;

Public cloud deployments;

Hyperscaler or enterprise on‑prem data centers;

National lab / supercomputer installations.

Manufactured but not yet racked/commissioned chips (e.g. sitting in warehouses) do not count as “installed.”

For purposes of this market, the resolver may use any combination of: shipment figures, press releases, investor disclosures, credible leaks, analyst estimates, and cluster‑level power specs to estimate when the cumulative installed capacity from that series clearly exceeds 1,000,000,000 W.

If only system‑level power is known (e.g. “this data center draws 1.5 GW for X GPUs”), the resolver may allocate that power to the series in a reasonable way based on configuration details.

Loop time (T_loop)

For a given qualifying series,

T_start = date of first fully working chip in silicon (as defined above).

T_1GW = date when worldwide installed capacity from that series first reaches or exceeds 1 GW.

T_loop is the number of calendar days between T_start and T_1GW, measured in UTC (or a consistent time standard).

A series qualifies for this market if T_loop ≤ 100 and T_1GW < 2032‑01‑01.

“New” series (only future chips count)

This market is about future hardware dynamics, not re‑evaluating past ramps.

A series only counts if its T_start is on or after the date this market is first created on Manifold.

Series whose first working chips clearly existed before market creation (e.g. current‑generation GPUs or TPUs) do not count, even if they might retrospectively have had a short loop.

Evidence standard and ambiguity

Strong evidence for YES:

To resolve YES, there must be a coherent, well‑documented case that:

(1) A particular series meets the definition above;

(2) There is a reasonably well‑pinned T_start; and

(3) There is very strong evidence that cumulative installed capacity from that series exceeded 1 GW at some date less than or equal to 100 days after T_start.

The evidence should be robust under conservative assumptions: even if you take the latest plausible T_start and the latest plausible date at which 1 GW is crossed, T_loop must still be ≤ 100 days.

Ambiguous or borderline cases:

If the best available evidence only allows a wide time window (e.g. “between early Q3 and late Q4 2031”) such that T_loop could be either ≤100 or >100 days depending on where within the window the true dates fall, the market should not resolve YES on that basis alone.

If no series clearly meets the threshold under conservative assumptions, the market resolves NO after January 1st 2032.

Multiple candidate series:

If several series plausibly meet the criterion, it is enough that at least one of them does.

The resolver does not need to identify which series was first, only that at least one series achieved T_loop ≤ 100 days with T_1GW before 2032‑01‑01.

Resolution timing

The market may resolve YES early if and when convincing public evidence emerges that the condition has been satisfied.

If, by shortly after January 1st 2032, there is no such strong evidence for any qualifying series, the market resolves NO.

In all cases, the final decision rests with the market creator / designated resolver, who should apply the definitions and conservative‑evidence standard above.