In his 2023 draft report on what a compute-centric framework says about takeoff speeds, Tom Davidson writes:

[If we use the suggested parameters], then even zillions of AGIs would only increase the pace of hardware progress by ~10X. But with billions of AGIs thinking 1000X as fast and optimising every experiment, I think progress could be at least 20X quicker than today, plausibly 100X.... I expect some people to favour larger numbers still.

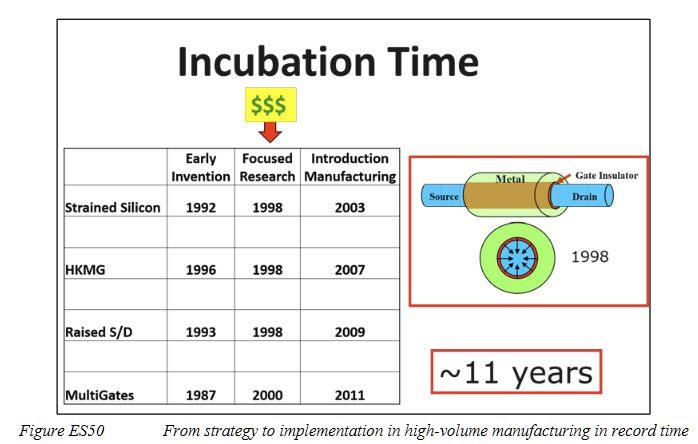

One way this might manifest is in faster times from invention to mass production. Historically, major front-end-of-line advances have reached production around 10-15 years after they were first demonstrated.

For example, the 2022 edition of the International Roadmap for Devices and Systems includes this figure (Executive Summary, p. 67):

Other examples of this claim: ExtremeTech ("The average length of time between when a new technological approach is introduced in a paper and when it hits widescale commercial manufacturing is on the order of 10–15 years"), James Clarke (Intel) ("Even if we come out on a two-year cadence for transistor technology, the development time for those technologies is 10 to 12 years."), BCG/Semiconductor Industry Association ("The average length of time between when a new technological approach is introduced in a research paper and when it hits widescale commercial manufacturing is estimated to be about 10–15 years, but it could be much longer than that for scientific breakthroughs that enable the current leading edge technologies.").

We might add shallow trench isolation (demonstrated ~1983, production in 1997 at 250nm) or use the 1998 FinFET instead of the more generic multigate demonstration. Current technologies on foundry roadmaps include gate-all-around FET (GAAFET, demonstrated ~2006, production ~2023 at Samsung 3nm) and complementary FET (CFET, demonstrated 2020, production ~2032 in imec's potential roadmap extension).

Resolution Criteria:

This market will resolve as YES if, before 1 January 2043,

A change to transistor structure comparable to the above examples reaches volume production in a leading-edge process node, and

It does so before the end of the 9th calendar year following the year that its first demonstration is reported at a conference or in a scientific journal.

For example, if Samsung, TSMC, or Intel were to use CFET in a new process node in volume manufacturing in 2029, this would resolve as YES.

I will use my own judgment as to whether a change is significant enough as well as on what counts as the first demonstration, together with industry reporting on what technologies foundries are using.

What would not count for the resolution criteria:

Smaller changes to existing processes or designs

Back-end-of-line changes

Risk production

Upgrades at trailing-edge process nodes

Adoption 10 years after "focused research" begins but 11 or more years since the first experimental demonstration

Forksheet FETs (demonstrated 2021) will not count if they follow nanosheet FETs, since they are a "natural extension", but if a foundry moved directly from FinFET to forksheets by the end of 2030, I would resolve the market as YES

I probably wouldn't count any experiments so far as precursor demonstrations to an eventual post-silicon process node that uses, for example, 2D transition-metal dichalcogenides or carbon nanotubes—both the dimensions and the fabrication processes should more closely resemble those eventually used in volume production.